A nova geração do Compute Express Link vai inaugurar um progresso relevante no ecossistema de interconexão de memória, dobrando a banda efetiva e migrando para o padrão PCIe 7.0, que agora se torna a base obrigatória para a especificação.

A mudança altera o planejamento de hardware para Data Centers e acelera a corrida por plataformas capazes de lidar com cargas de IA e computação heterogênea em grande escala.

Para que serve o CXL na prática?

O CXL (Compute Express Link) foi criado para resolver um gargalo clássico dos sistemas modernos: a dificuldade de diferentes componentes trocarem dados rapidamente e de forma coerente, sem duplicação de memória e sem depender apenas da CPU como mediadora.

À medida que servidores passam a combinar CPUs, GPUs, aceleradores de IA, DPUs, FPGAs e camadas de memória em múltiplos formatos, o fluxo de dados precisa ser mais eficiente que o fornecido por interconexões tradicionais.

Na essência, o CXL atua como uma ponte de alta velocidade com coerência de memória, permitindo que vários dispositivos acessem e compartilhem o mesmo espaço de memória sem cópias desnecessárias. Isso reduz latência, melhora o uso de memória total disponível e viabiliza arquiteturas mais flexíveis.

O padrão foi pensado para três grandes funções:

1. Expansão de memória sem alterar a CPU

Com o CXL, é possível adicionar módulos externos de memória que se conectam diretamente à CPU ou a um switch CXL. Isso cria um “pool” expansível que pode ser redistribuído conforme a carga.

Assim, Data Centers ganham a capacidade de ajustar memória dinamicamente, evitando desperdício e reduzindo custos operacionais.

2. Compartilhamento de memória entre vários dispositivos

A grande virada do CXL está em permitir que aceleradores de IA, GPUs e outros dispositivos acessem a mesma região de memória com coerência, algo que elimina o trabalho de copiar dados entre buffers diferentes.

Em aplicações de IA, por exemplo, isso ajuda modelos grandes a serem processados por múltiplos chips simultaneamente, com comunicação mais fluida.

3. Interconexão coerente para computação heterogênea

Servidores modernos raramente trabalham apenas com CPU. A tendência é que tarefas intensivas migrem para aceleradores especializados.

O CXL cria uma base comum de interconexão para que esses componentes atuem como partes de um único sistema lógico. Isso é especialmente relevante em:

- treinamento e inferência de modelos de IA

- HPC (computação de alto desempenho)

- bancos de memória elástica

- bancos de dados in-memory

- workloads altamente paralelos

Graças à coerência integrada, todos os dispositivos mantêm visão sincronizada dos dados, sem disputas ou inconsistências.

Por que isso se tornou tão importante agora?

Com o crescimento da IA generativa, modelos cada vez maiores exigem quantidades extensas de memória acessível.

A estratégia atual de empilhar módulos de DRAM no mesmo soquete está chegando ao limite físico e térmico. O CXL surge como alternativa escalável, permitindo construir servidores com:

- memória desagregada, compartilhada entre racks

- topologias flexíveis, usando switches e níveis adicionais de fabric

- mais largura de banda por enlace, agora ampliada com o CXL 4.0

- latência controlada, mesmo com múltiplos dispositivos no caminho

Desta forma, teremos uma arquitetura pronta para lidar com cargas massivas de processamento, sem exigir mudanças completas no desenho das CPUs.

CXL 4.0 muda de patamar para largura de banda

O CXL Consortium publicou formalmente a especificação CXL 4.0, que passa de 64 GT/s para 128 GT/s, apoiando-se diretamente na interface PCIe 7.0 como camada física.

Isso representa o maior salto desde a criação do padrão e consolida o CXL como eixo central de arquiteturas que combinam CPUs, GPUs, aceleradores e camadas de memória variadas.

Segundo o documento oficial , a evolução mantém o formato de flit de 256 Bytes, acrescenta modo nativo x2, viabiliza até quatro retimers por canal e entrega melhorias relevantes de RAS, como visibilidade mais ampla de erros e mecanismos avançados de manutenção.

A liberação do CXL 4.0 faz parte de um novo estágio na conexão coerente de memória, ampliando a largura de banda e preservando compatibilidade com gerações anteriores, ao mesmo tempo em que prepara o setor para novos modelos de uso

Derek Rohde, presidente do consórcio

PCIe 7.0 passa a ser o núcleo obrigatório

A migração do CXL para PCIe 7.0 não é simbólica. Na prática, ela confirma que o ecossistema de servidores, placas-mãe, aceleradores e controladores terá de avançar para uma plataforma completamente alinhada ao novo barramento. O padrão se torna, portanto, pré-requisito para qualquer implementação real de CXL 4.0.

A dependência impacta diretamente fornecedores de hardware que ainda estão estabilizando produtos com PCIe 5.0 e planejando a chegada do PCIe 6.0.

A nova especificação indica que a janela de adoção pode se acelerar, especialmente em segmentos como IA generativa, HPC e bancos de memória desagregada.

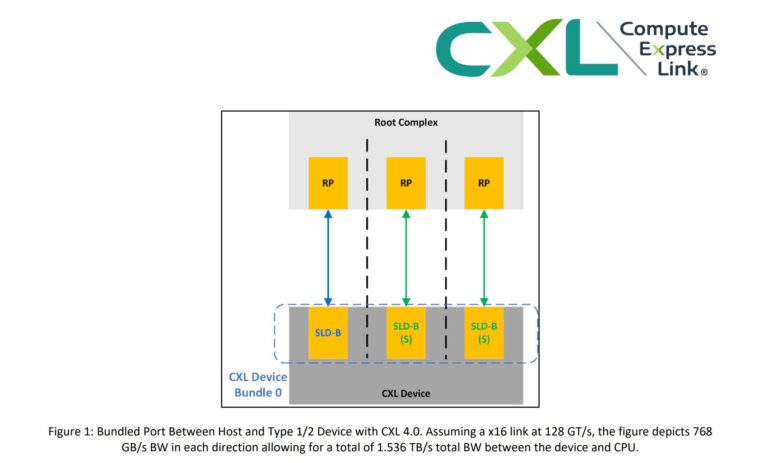

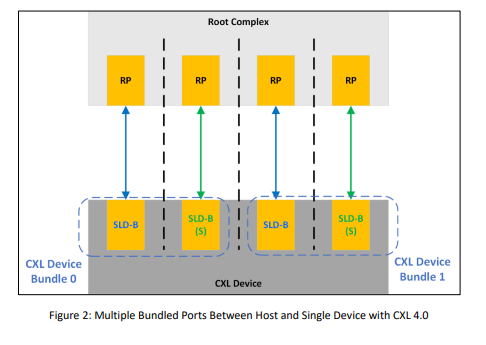

Bundled Ports criam novas possibilidades entre hosts e aceleradores

Um dos recursos mais comentados do CXL 4.0 é o Bundled Port, que permite combinar dois enlaces físicos para ampliar a banda efetiva entre host e dispositivos tipo 1/2. Isso facilita o uso de aceleradores de IA, DPUs e placas híbridas que precisam transmitir grandes volumes de dados com latência controlada.

A funcionalidade também sinaliza uma aproximação maior entre o CXL e arquiteturas de interconexão que trabalham com agregação de links, algo crítico para sistemas modulados e servidores otimizados para workloads paralelos.

Memória com níveis avançados de confiabilidade

O CXL 4.0 avança nos recursos de RAS ao tornar a manutenção mais granular, permitindo operações como:

- correção e isolamento mais eficiente de falhas

- reparos iniciados pelo host logo no boot

- opções mais flexíveis de memory sparing

- maior visibilidade no diagnóstico de inconsistências

As adições reforçam o conceito de memória compartilhada e expansível, reduzindo gargalos em cenários de pooling ou tiering.

Compatibilidade segue preservada

Apesar da mudança para PCIe 7.0, o consórcio manteve compatibilidade total com CXL 1.x, 2.0 e 3.x, algo fundamental para fabricantes que dependem de ciclos longos de desenvolvimento.

A estratégia preserva investimentos de gerações anteriores e facilita combinações de dispositivos, retimers e switches em Data Centers híbridos, típicos de grandes provedores de nuvem.

Comparativo técnico: evolução do CXL

Com base nos dados exibidos pela VideoCardz e no documento oficial do CXL Consortium, a evolução entre as versões pode ser resumida assim:

| Categoria | CXL 1.1 | CXL 2.0 | CXL 3.0 | CXL 4.0 |

|---|---|---|---|---|

| Banda máxima | até 32 GT/s | até 32 GT/s | até 64 GT/s | 128 GT/s |

| Base PCIe | PCIe 5.0 | PCIe 5.0 | PCIe 6.0 | PCIe 7.0 |

| Formato de flit | sem flit fixo | sem flit fixo | 256 Bytes | 256 Bytes mantido |

| Memória / RAS | expansão simples | adiciona pooling | gestão avançada e coerência melhorada | RAS aprimorado, maior visibilidade de erros, modo x2 |

| Fabric / Interconexão | ponto a ponto | switches e pooling | topologias multinível | Bundled Ports, até 4 retimers, maior alcance |

| Compatibilidade | apenas 1.1 | compatível com 1.1 | compatível com 2.0 e 1.x | compatível com 3.x, 2.0 e 1.x |

Além disso, a nova especificação integra suporte a switching multinível, ampliando arquitetura para topologias mais densas.

Avanço refina Data Centers modernos

Com a multiplicação de workloads de IA e a necessidade de transportar grandes volumes de dados entre chips heterogêneos, o CXL 4.0 chega como peça estratégica na construção de servidores escaláveis.

A dependência de PCIe 7.0 também funciona como um acelerador da próxima geração de plataformas, empurrando OEMs e fabricantes de processadores para ciclos de atualização mais rápidos.

Leia também:

- Novo SSD PCIe 5.0 da TeamGroup alcança até 14.900MB/s de velocidade

- Novo microSSD PCIe Gen4 une desempenho extremo e design ultracompacto

- MSI lança placa-mãe MPG X870I EDGE TI EVO WiFi com suporte a memórias de até 10.000 MT/s

Rumo a uma era de interconexão mais ambiciosa

O lançamento da especificação 4.0 não fecha um ciclo, mas abre uma corrida por soluções capazes de absorver essa largura de banda e explorar a nova lógica de fabric coerente.

Assim que PCIe 7.0 ganhar tração, o CXL tende a se tornar o elo mais visível entre CPU, aceleradores de IA e camadas de memória cada vez mais distribuídas.

Fonte: Compute Express Link